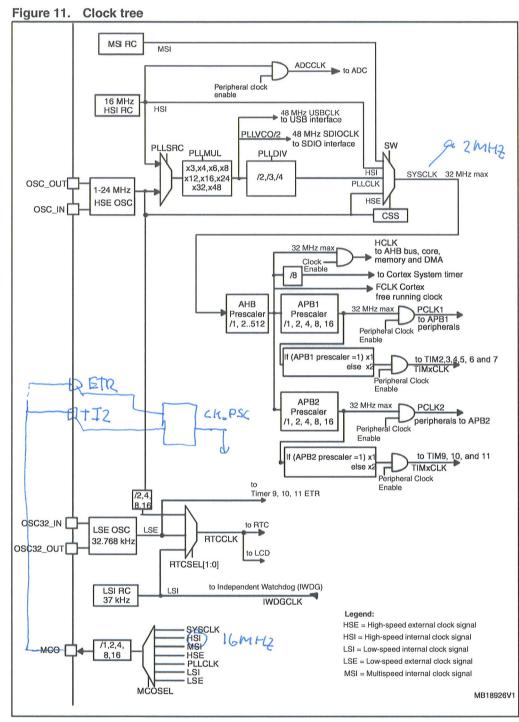

For full details about the internal and external clock source characteristics, please refer to the "Electrical characteristics" section in your device datasheet.

> TIM3\_ETR TIM4\_ETR DOCID 15965 Rev 5

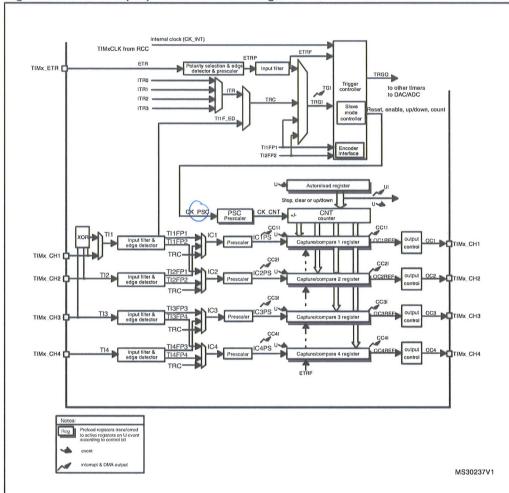

Figure 80. General-purpose timer block diagram

## 16.3 TIM2 to TIM5 functional description

## 16.3.1 Time-base unit

The main block of the programmable timer is a 16-bit/32-bit counter with its related autoreload register. The counter can count up but also down or both up and down. The counter clock can be divided by a prescaler.

The counter, the auto-reload register and the prescaler register can be written or read by software. This is true even when the counter is running.

The time-base unit includes:

- Counter Register (TIMx\_CNT)

- Prescaler Register (TIMx\_PSC):

- Auto-Reload Register (TIMx\_ARR)

The counter can count at each rising or falling edge on the external trigger input ETR.

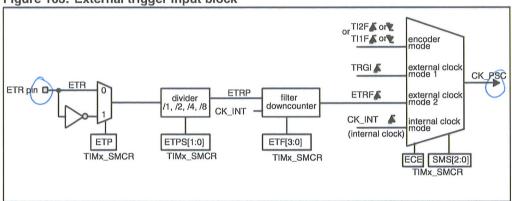

Figure 103 gives an overview of the external trigger input block.

Figure 103. External trigger input block

For example, to configure the upcounter to count each 2 rising edges on ETR, use the following procedure:

- 1. As no filter is needed in this example, write ETF[3:0]=0000 in the TIMx\_SMCR register.

- 2. Set the prescaler by writing ETPS[1:0]=01 in the TIMx\_SMCR register

- Select rising edge detection on the ETR pin by writing ETP=0 in the TIMx\_SMCR register

- 4. Enable external clock mode 2 by writing ECE=1 in the TIMx\_SMCR register.

- 5. Enable the counter by writing CEN=1 in the TIMx\_CR1 register.

The counter counts once each 2 ETR rising edges.

The delay between the rising edge on ETR and the actual clock of the counter is due to the resynchronization circuit on the ETRP signal.

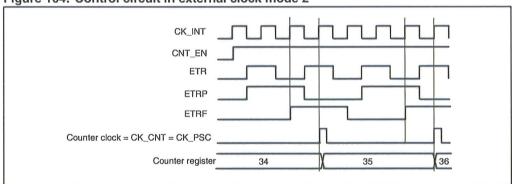

Figure 104. Control circuit in external clock mode 2

## 16.3.4 Capture/compare channels

Each Capture/Compare channel is built around a capture/compare register (including a shadow register), a input stage for capture (with digital filter, multiplexing and prescaler) and an output stage (with comparator and output control).

The following figure gives an overview of one Capture/Compare channel.

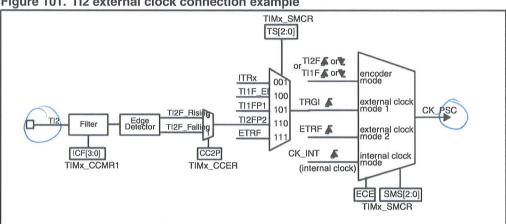

Figure 101. TI2 external clock connection example

For example, to configure the upcounter to count in response to a rising edge on the TI2 input, use the following procedure:

- Configure channel 2 to detect rising edges on the TI2 input by writing CC2S= '01 in the TIMx CCMR1 register.

- Configure the input filter duration by writing the IC2F[3:0] bits in the TIMx\_CCMR1 register (if no filter is needed, keep IC2F=0000).

Note:

The capture prescaler is not used for triggering, so you don't need to configure it.

- Select rising edge polarity by writing CC2P=0 and CC2NP=0 in the TIMx\_CCER register.

- 4. Configure the timer in external clock mode 1 by writing SMS=111 in the TIMx\_SMCR register.

- Select TI2 as the input source by writing TS=110 in the TIMx\_SMCR register. 5.

- Enable the counter by writing CEN=1 in the TIMx\_CR1 register.

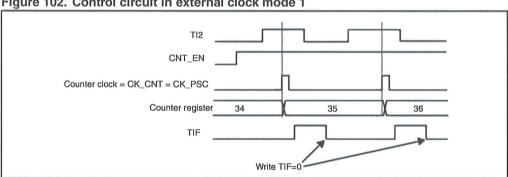

When a rising edge occurs on TI2, the counter counts once and the TIF flag is set.

The delay between the rising edge on TI2 and the actual clock of the counter is due to the resynchronization circuit on TI2 input.

Figure 102. Control circuit in external clock mode 1

## External clock source mode 2

This mode is selected by writing ECE=1 in the TIMx\_SMCR register.